1000804 有關第 94104892N01 號「在一銲墊下之低電容靜電放電保護 結構」發明專利舉發事件 (99 年度行專訴字第 143 號) (判決日: 100.3.10.)

爭議標的: 進步性專利要件

**系爭專利:** 「在一銲墊下之低電容靜電放電保護結構」發明專利

相關法條: 專利法第22條第4項規定

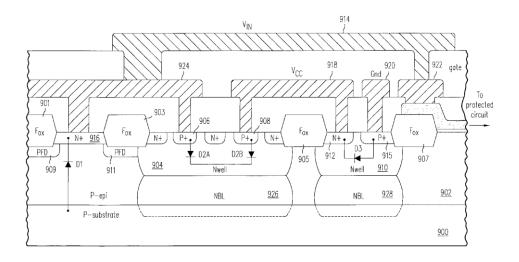

判決要旨:一、證據 2 之擴散體 912 係位於 N 井,擴散體 916 係位於 P 井, 二者係屬不同的擴散體結構,與系爭專利之第二較重摻雜的 n型矽擴散體(N+擴散體)均係位於 P 井中, 二者結構顯然互 異。再者,系爭專利之第二 N+擴散體係圍繞該第一 N+擴散 體;惟證據2之圖9A並未揭示擴散體912及擴散體916圍 繞第一 N+擴散體之結構。·····證據 2 之 P+擴散體 908, 906 係連接兩個不同之銲墊,與系爭專利之複數個 P+擴散體連接 一銲墊不同。又系爭專利之第二 N+擴散體係連接至一連接, 而證據 2 之擴散體 912 藉由金屬層 918 連接至 VCC, 而擴散 體 916 藉由金屬層 924 連接至金屬層 914 再連接至 VIN,因 VIN 與 VCC 兩不同電壓,故金屬層 924 與金屬層 914 為兩不 同之金屬層之連接,與系爭專利之第二 N+擴散體係連接至一 連接,為不同之連接結構。……證據3雖揭示 N+(620,624) 形成於 N 井並將 N 井重疊進 P 井 21,惟其並未揭示構件 620 及 624 圍繞 622 之結構,亦未揭示構件 616 及 628 圍繞 620 及624之技術特徵。

二、證據2之P+(908)與N+擴散體及證據3之P+(622)與N+(620,624)之連接方式不同,故其結合上即有困難……雖證據2及證據3均為ESD電路結構,惟從事半導體電路製造設計領域者皆知,電路結構佈設不同,或元件間之連接關係(方式)不同,其效果則會不同,因證據2及證據3與系爭專利間存在前述之差異,故證據2及證據3之結合上並非明顯,且證據2及證據3均未揭示系爭專利之第二N+擴散體(128b)圍繞第一N+擴散體(128a)之技術特徵。故證據2及證據3之組合尚無法證明系爭專利請求項1、18及28項不具進步性。

# 【判決摘錄】

- 一、兩造主張

- (一)原告主張

- 1. 系爭專利之技術特徵與證據 2 之技術特徵不同:

- (1)系爭專利是關於在銲墊(bondpad)下低電容靜電放電(ESD)之保護 結構。系爭專利提供一種整合於積體電路晶粒內的 ESD 保護電路, 對於保護敏感的輸入及/或輸出電路係有效的,且具有低電容。系 爭專利提供一實質上位於積體電路銲墊下、具有低電容並能承受高 電流放電事件的 ESD 保護結構。證據 2 係關於一 ESD 保護電路,其 允許該輸出信號升高至相對於供應電源上之一選擇距離且不會觸 發該 ESD 電路。證據 2 允許該輸出信號下落至相對於接地電位之一 選擇距離且也不會觸發該 ESD 電路。

- (2)證據 2 之元件 918 及 924 係金屬層,非如系爭專利之銲墊,證據 2 完全沒有揭示任何態樣之銲,此由證據 2 可知:「N+ region 916 (cathode of diode D1) and P+ region 906 (anode of diode D2A) are connected via a metal layer 924 which makes contact with an upper metal layer 914 to which VIN in connected. …The supply voltage VCC is delivered to P+ region 908 (anode of diode D3) and N+ contact region 912 (cathode of diode D3) through a metal layer 918」。因此,證據 2 之 918 及 924 顯然為金屬連接,訴願理由認定 918 及 924 為結合墊顯為錯誤。

- (3)訴願理由認定證據 2<sup>「</sup>結合墊 918 及 924 連接至該複數個 P+重摻雜」,根據證據 2 之圖 8A 及 8B,訴願理由顯然認定因為金屬層 914 連接至 VIN 且金屬層 918 連接至 VCC,該金屬層 918 及 924 連結至一結合墊。惟查:證據 2 無法確認該等電壓為內部或外部電壓,證據 2 並未揭示系爭專利所述「一銲墊,其係連接至該等複數個 P+擴散體」之技術特徵,證據 2 充其量僅揭示 P+擴散體 906 透過 918 與 924 耦合至一結合墊,而系爭專利則為複數個 P+擴散體連接至該銲墊。由於證據 2P+擴散體 908 並未同時連接至金屬層 918 及 924,因此並非連接至該相同之結合墊。故可知,證據 2 完全未揭示系爭專利關於銲墊之技術特徵。

- (4)證據 2 中元件 912 非配置於 p 型矽井中, 而是在 N-井 910 中, 且證據 2 無任何元件 916 圍繞 (surround) 元件 904 之敘述。

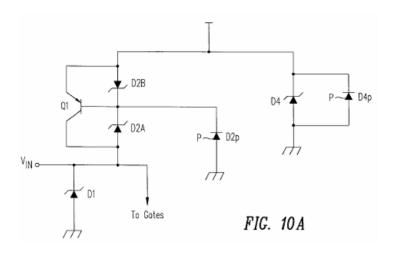

- (5)證據 2 說明書圖式第 9A 圖及第 6 欄第 55 至 57 行敘述,N+區域 916 形成二極體 D1,以及二極體 D3 與區域 912 及 915 形成於 N-井 910 中。依照此一結構,區域 912 必然侷限於 N-井 910 中以形成二極體 D3,而區域 916 則明顯地在 N-井 910 外部。訴願決定認為 912 及 916 係連接在一起而圍繞該第一 N+重摻雜,如此,該二極體 D1 及 D3 之陰極必然連接在一起。然而,證據 2 圖式第 10A 圖顯示此一相 等之電路。在此相等之電路中顯示該二極體 D1 之陰極並未連接至 該二極體 D3 之陰極係與 VCC 耦接,而該二極體 D1 之陰極係與 VIN 耦接,如證據 2 圖式第 10A 圖所示,該等

陰極係耦接至不同之電位,故 912 及 916 並未連接在一起以圍繞結構 904。因此,區域 912 及 916 非如訴願決定所認定為「圍繞第一N+重摻雜」。

(6)系爭專利與證據2間主要不同之結構如下:

|     | 系爭專利                                       | 證據 2                                                                       |

|-----|--------------------------------------------|----------------------------------------------------------------------------|

| (1) | 位於該P-井中之第二<br>  較重摻雜的 n 型矽擴散<br>  體(N+擴散體) | 第二較重摻雜的 n 型矽  <br>擴散體 (N+擴散體) 事  <br>實上位於 N-井                              |

| (2) | 該第二 N+擴散體圍繞該<br>  第一 N+擴散體                 | 該第二 N+擴散體並未  <br>  繞該第一 N+擴散體                                              |

| (3) | 一銲墊,其係連接至該<br>  等複數個 P+擴散體<br>             | 無銲墊。即便確實有焊  <br>墊存在於某處,至少需  <br>要二個銲墊分別連接至<br>複數個 P+擴散體,而非  <br>系爭專利所稱的一銲墊 |

| (4) | 一連接,其係連接至該<br> 第二N+擴散體                     | 至少二個連接,而非系   爭專利所稱的一連接                                                     |

## (7)系爭專利與證據 2 之差異, 說明如下:

- i. 系爭專利之第二較重摻雜的 N+擴散體係位於該 P-井中,而舉發人所指證據 2 之第二 N+擴散體 912 則位於 N-井 910 中,與系爭專利的 N+擴散體係位於 P-井中不同。舉發理由就證據 2 之認知,顯然有嚴重錯誤。系爭專利中第二 N+擴散體之結構顯然不同於證據 2 之結構。

- ii. 系爭專利第二 N+擴散體呈現一圍繞之結構,而證據 2 之第二 N+ 擴散體 916 並未圍繞該 N-井 904 中之第一 N+擴散體。

- iii.舉發人指稱證據 2 之第二 N+擴散體為 912 及 916,然而,N+擴散體 912 及 N+擴散體 916 為兩不同擴散體,舉發人主張並非可採。即便舉發人認定 916 為第二 N+擴散體,而 912 為除了第一與第二 N+擴散體以外之另一 N+擴散體,然而證據 2 未揭示二個不同的 N+ 擴散體 912 及 916 共同圍繞第一 N+擴散體。

- iv. 證據 2 並未提及如系爭專利所述銲墊之結構,證據 2 之元件結合 墊 918 及 924 僅係金屬層。縱使舉發人認為結合墊 918 及 924 即

為系爭專利所述之銲墊,結合墊918及924係為兩不同銲墊,而 系爭專利則僅具有一銲墊,故證據2與系爭專利顯然不同。

- v. 證據 2 之複數個 P+擴散體係連接至不同的金屬層, 而系爭專利之 複數個 P+擴散體則連接至單一銲墊。

- vi.即便證據 2 結構可連接在某處之銲墊,基於證據 2 說明書及圖式 之敘述,由於 VIN 不同於 VCC,故證據 2 至少包括二個銲墊,而 系爭專利則僅具有一銲墊,二者仍然不同。

- VII.由於系爭專利第二 N+擴散體具有圍繞之結構,系爭專利可藉由一連接而連接至該第二 N+擴散體。相較而言,由於證據 2 之第二 N+ 擴散體沒有圍繞結構,且 912 不同於 916,因此至少有二個不同 的連接而分別連接至 912 及 916。

- (8)綜上所述,證據2與系爭專利之結構顯然不相同,且證據2完全未 揭示系爭專利之技術特徵,系爭專利相較於證據2自具有進步性。

- 2. 系爭專利之技術特徵與證據 3 不同:

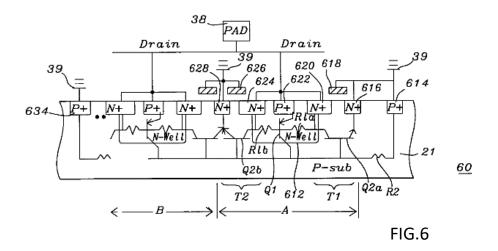

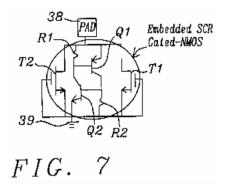

- (1)證據 3 揭示一個嵌入式寄生矽控整流器 (parasitic silicon controlled rectifier, parasitic SCR) 保護裝置,用於利用在汲極邊插入一 P+擴散體及一 N-井以保護一晶片或一輸出銲墊,其中該 汲極之部份形成一低觸發 SCR。該裝置之布局使得該汲極連接在該 P+擴散體及該 N+汲極處緊綁一起,讓連接非常短;藉此防止閂鎖 (latch-up)。

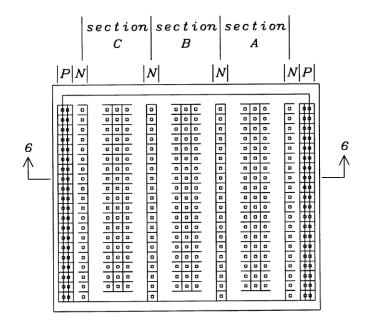

- (2)證據 3 揭示一保護電路,如圖 5 及 6 所示。惟證據 3 亦無揭示結構元件 616 及 628 圍繞 N-井結構 612,相反的,證據 3 中每個結構均為位於該 N-井 612 各邊之條帶。結構元件 620 及 624 為分開的結構,並無圍繞該 P+結構 622;此三個結構均為條帶狀,並被配置為彼此相鄰,故證據 3 未揭示系爭專利之技術特徵。

- (3)由於證據3完全無法揭示系爭專利之技術特徵或結構,即便結合其 他任何證據(如證據2),也無法否定系爭專利之可專利性。

- 3. 證據 2 與證據 3 之結合顯非輕易可得:

- (1)本案中證據 3 之元件 620、622 及 624 均為條帶狀且彼此相鄰,此一 結構完全不同於證據 2 之結構。

- (2)據證據 3 說明書所述,證據 3 主要技術特徵之一在於在 P+擴散體之 汲極與 N+汲極係連接在一起。因此,元件 620、622 及 624 均藉由傳 導構件而連接至晶片墊 38 而具有相同之電位。相較於證據 2,由於 N+擴散體係在元件 904 中浮動,元件 906(P+)係經由一金屬層 924 連 接至元件 916(N+),且元件 908(P+)係經由一金屬層 918 連接至元件 912(N+),故可知元件 904 中之 N+擴散體、元件 906 及 908 顯然具有 不同之電位。為實施證據 3 之發明,在 P+擴散體之汲極與 N+汲極必 須連接在一起,而此結構與證據 2 完全不同。該發明所屬技術領域

具有通常知識者欲實施證據 2 之發明時,完全不會考慮證據 3 之結構或技術特徵。

- (3)由於證據2與證據3之結構完全不相同且彼此不相容,證據2與證據3之結合顯然不易,甚至完全無法結合。訴願理由不察,逕謂證據2與證據3「其間技術結合並非困難」,其顯然有違前揭專利審查基準之規定。

- (4)退萬步言,由於證據2及證據3個別均未能揭示系爭專利之技術特徵,故縱然證據2及證據3可結合(原告仍否認之),其結合後之結果亦無法證明系爭專利不具進步性。

- 4. 系爭專利之技術特徵與證據 4 之技術特徵不同:

- (1)證據 4 揭示一個輸出緩衝器,其包含一拉高電路及一拉低電路;其中該拉低電路具有一電阻,一二極體及一靜電保護元件。系爭專利則為在銲墊下之低電容靜電放電(ESD)保護結構之技術特徵。

- (2)證據 4 僅揭示一具有靜電保護元件之輸出緩衝器,其無揭示任何關於在銲墊下之低電容靜電放電保護結構,證據 4 明顯與系爭專利不同。

- 5. 系爭專利之技術特徵與證據 5 之技術特徵不同:

- (1)證據 5 欲解決之問題為即使在供應電源及接地端點之間加入保護電路,在半導體電路的內部元件仍常常損壞。證據 5 之發明中,因於具有負電位的靜電的施加,就可以使進入到接地端點 TG 一側來的電荷易於通過電源端點 TV 向電源電壓 Vcc 放出,就可以防止內部元件因靜電引起之損壞。

- (2)證據5提供一保護電路,其可導向在電源端點及接地端點之間的電荷,亦無揭示任何關於在銲墊下之低電容靜電放電保護結構,明顯的與系爭專利不同。

- 6. 系爭專利之技術特徵與證據 6 之技術特徵不同:

- (1)證據 6 揭示一薄膜電晶體,用於一抗靜電電路及防止接面漏電流 (junction-leakage current)。

- (2)證據 6 僅揭示一用於抗靜電電路及防止接面漏電流之薄膜電晶體, 其無揭示任何關於在銲墊下之低電容靜電放電保護結構,明顯的與 系爭專利不同。

- 7. 系爭專利之技術特徵與證據7之技術特徵不同:

- (1)證據7揭示一種半導體裝置的靜電保護電路及其結構。證據7特徵 在於該半導體裝置可與一銲墊連接,而該靜電保護結構用在一在電 晶體汲極擴散區之淺摻雜電阻或擷取電阻,以使在靜電電壓從該銲 墊輸入時,在該電阻處產生壓降,進而形成一寄生雙極電晶體,以 傳導因該靜電放電產生之電流。

- (2)證據7僅揭示一靜電保護電路,其無揭示任何關於在銲墊下之低電 容靜電放電保護結構,明顯的與系爭專利不同。

- 8. 系爭專利之技術特徵與證據 8 之技術特徵不同:

- (1)證據 8 揭示之靜電放電 (ESD) 保護組件,其可被串接以提高 ESD 保護組件的總維持電壓且避免鬥鎖。

- (2)證據 8 僅揭示一可被串接之靜電保護組件,其無揭示任何關於在銲墊下之低電容靜電放電保護結構,明顯與系爭專利不同。

- 9. 系爭專利之技術特徵與證據 9 之技術特徵不同:

- (1)證據 9 揭示一形成於一井中之保護電路,且與埋層連接。為改良保護雙極電晶體被晶片佈局及晶片雜質濃度的影響,證據 9 提供一靜電損壞保護裝置,其具有高靜電崩潰阻抗,高門鎖電阻抗以及良好的保護能力。

- (2)證據 9 僅揭示一形成於井中且與埋層連接之保護電路,其無揭示任何關於在銲墊下之低電容靜電放電保護結構,明顯的與系爭專利不同。

- 10. 系爭專利之技術特徵與證據 10 之技術特徵不同:

- (1)證據 10 揭示一靜電放電保護電路及其佈局;其中至少在電極墊及接 地線之間具有一個靜電放電保護電路。

- (2)證據 10 僅揭示一在電極墊及接地線之間之靜電放電保護電路,其無揭示任何關於在銲墊下之低電容靜電放電保護結構,明顯的與系爭專利不同。

- 11. 系爭專利之技術特徵與證據 11 之技術特徵不同:

- (1)證據 11 揭示一用於半導體輸入裝置的靜電放電保護之製造方法。證據 11 提供一保護電路用於限制靜電電壓至一安全位準,且不破壞欲保護之電路及保護電路本身。在證據 11 之發明中,小靜電電壓被利用以產生電荷載體,其可用於觸發一蕭特基夾鉗二極體 (Schottky clamp diode),藉此限制該靜電電壓至一低於 100 伏特崩潰電壓之大小。

- (2)證據 11 僅揭示一利用觸發蕭特基夾鉗二極體之靜電放電保護方法, 其無揭示任何關於在銲墊下之低電容靜電放電保護結構,明顯的與 系爭專利不同。

- 12. 因此,證據2至11 與系爭專利利用不同的方法以解決不同的問題,為明顯不同的發明。該發明所屬技術領域具有通常知識者並無任何動機將證據2至11 予以結合,更無法將其據以實施。即便將證據2至11 之技術特徵結合,其亦無揭示系爭專利所載之技術特徵,例如「一位於該N-井中之第一較重摻雜的n型矽擴散體(N+擴散體),其中該第一N+擴散體圍繞該等複數個P+擴散體,並將該N-井重疊進該P-井」。

13. 原處分除如同訴願決定般具有相同之謬誤外,原處分機關尚且錯誤認定:「證據3已揭示證據2未有揭示之技術特徵為兩造所不爭執」,並據以作成原處分。然原告從未主張「證據3揭示證據2所未揭示之系爭案之其他技術特徵及結構」,原處分機關所據以作成原處分之事實顯然有誤。關於此一謬誤,原告已於訴願程序中詳加說明,惟原訴願機關不採,仍逕自認定證據2及證據3已揭示系爭案之大部分技術特徵,原訴願機關之認定亦有不當。

## (二)智慧局主張

- 1. 起訴理由稱舉發證據 2、3 有無法結合之情事,此為原告自行判斷所生之誤認,原處分理由(四)已載「…相較系爭專利第 1 項所載之技術特徵,證據 2 未有揭示該第一 N+擴散體圍繞該等複數個 P+擴散體,並將該 N-井重疊進該 P-井,證據 3 已揭示證據 2 未有揭示之技術特徵,為兩造所不爭執,專利權人答辯稱舉發理由未有詳載如何結合證據 2、3 所揭示,惟證據 2、3 已揭示系爭專利請求項第 1 項技術特徵,其間技術結合並非困難,以證據 2 所揭示在形成系爭專利請求項 1 之該第一 N+擴散體圍繞該等複數個 P+擴散體,並將該 N-井重疊進該 P-井時,將證據 3 所揭示該 N+重摻雜 624 重疊形成於 N 井層,該 N 井則重疊形成於 P 井 21。據此,結合證據 2、3 可證明系爭專利請求項第 1 項為所屬該項技術領域具有通常知識者所能輕易完成。 • • 」,並非如原告所稱證據 2、3 間有無法結合之情事。

- 2. 起訴理由所稱僅為原告逕以系爭專利與舉發證據進行比對之主觀論述, 然系爭專利申請專利範圍各項已為舉發證據所揭示不具專利要件,原處 分均已詳載理由,不另贅述。

## 二、本案爭點

- (一)舉發證據 2 結合舉發證據 3 可否證明系爭專利申請專利範圍第 1、18 及 28 及 8-14、17、19-24 及 27 項不具進步性?

- (二)舉發證據2結合舉發證據3、4-11 可否證明系爭專利申請專利範圍第 2項不具進步性?

- (三)舉發證據 2 結合舉發證據 3、4 或 9 可否證明系爭專利申請專利範圍 第 3 項不具進步性?

- (四)舉發證據2結合舉發證據3、4可否證明系爭專利申請專利範圍第4、 16及26項不具進步性?

- (五)舉發證據 2 結合舉發證據 3、4 或 10 可否證明系爭專利申請專利範圍 第 5-7 項不具進步性?

- (六)舉發證據 2 結合舉發證據 3、5、7、11 可否證明系爭專利申請專利範 圍第 15、25 項不具進步性?

# 三、判決理由

- (一)系爭專利請求項之技術內容 系爭專利申請專利範圍共有28項,其中第1、18、28項為獨立項, 其餘為附屬項。其內容為:

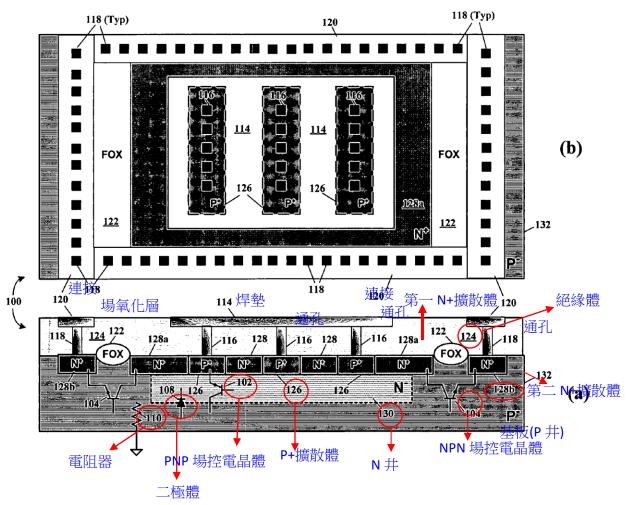

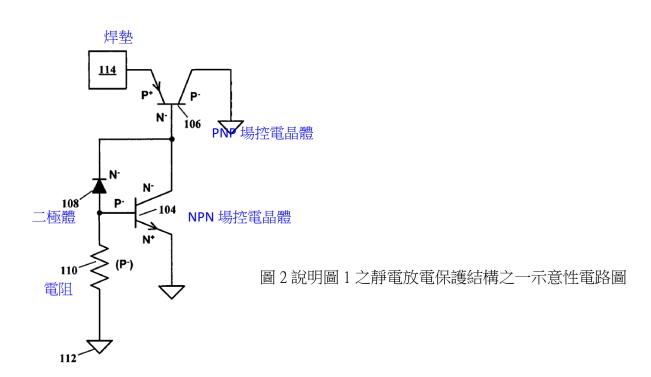

- 1. 一種靜電放電保護結構(100),其包含:一積體電路,其具有一較輕摻雜的 p型矽井(P-井)(132);一位於該 P-井(132)中之較輕摻雜的 n型矽井(N-井)(130);複數個位於該 N-井(130)中之較重摻雜的 p型矽擴散體(P+擴散體)(126);一位於該 N-井(130)中之第一較重摻雜的 n型矽擴散體(N+擴散體)(128,128a),其中該第一 N+擴散體(128,128a)圍繞該等複數個 P+擴散體(126),並將該 N-井(128a)重疊進該 P-井(132);一位於該 P-井(132)中之第二較重摻雜的 n型矽擴散體(N+擴散體)(128b),該第二 N+擴散體(128b)圍繞該第一 N+擴散體(128a);一銲墊(114),其係連接至該等複數個 P+擴散體(126);以及一連接(120),其係連接至該第二 N+擴散體(128b)。

- 2. 如請求項1之靜電放電保護結構,其中該P-井係該積體電路基板。

- 3. 如請求項 1 之靜電放電保護結構,其進一步包含一位於該等第一與第二 N+擴散體之間的場氧化物。

- 4. 如請求項 1 之靜電放電保護結構,其進一步包含該積體電路之一較輕 摻雜的 n 型矽基板(N-基板),其中該 P-井係在該 N-基板中。

- 5. 如請求項 1 之靜電放電保護結構,其中該複數個 P+擴散體為帶形。

- 6. 如請求項1之靜電放電保護結構,其中該複數個P+擴散體為矩形。

- 7. 如請求項1之靜電放電保護結構,其中該複數個P+擴散體為方形。

- 8. 如請求項1之靜電放電保護結構,其中該銲墊係使用一第一複數個導電通孔連接至該等複數個P+擴散體。

- 9. 如請求項1之靜電放電保護結構,其中連接至該第二 N+擴散體之該連接係使用一第二複數個導電通孔。

- 10. 如請求項 8 之靜電放電保護結構,其中第一複數個導電通孔為金屬。

- 11. 如請求項 8 之靜電放電保護結構,其中第一複數個導電通孔包含導電半導體矽。

- 12. 如請求項 9 之靜電放電保護結構,其中該第二複數個導電通孔為金屬。

- 13. 如請求項 9 之靜電放電保護結構,其中該第二複數個導電通孔包含導電矽。

- 14. 如請求項1之靜電放電保護結構,其進一步包含一第二連接,其使用一第三複數個導電通孔連接至該第一N+擴散體。

- 15. 如請求項1之靜電放電保護結構,其中該P-井係耦合至接地。

- 16. 如請求項 1 之靜電放電保護結構,其中該 P-井係耦合至一共用的電源供應軌。

- 17. 如請求項1之靜電放電保護結構,其中該等複數個 P+擴散體、該第 N+擴散體以及該 N-井係實質上位於該銲墊之下。

- 18. 一種靜電放電保護結構(100),其包含:一積體電路,其具有一較輕摻雜的 p型矽井(P-基板)(132);一位於該 P-基板中之較輕摻雜的 n型矽井(N-井)(130);複數個位於該 N-井(130)中之較重摻雜的 p型矽擴散體(P+擴散體)(126),其中該複數個 P+擴散體為矩形;一位於該 N-井(130)中之第一較重摻雜的 n型矽擴散體(N+擴散體)(128a),其中該第一 N+擴散體圍繞該複數個 P+擴散體(126),並將該 N-井重疊進該 P-井(132);一位於該 P-基板(132)中之第二較重摻雜的 n型矽擴散體(N+擴散體)(128b),其中該第二 N+擴散體圍繞該第一 N+擴散體(128a);一場氧化物(122),其位於該等第一與第二 N+擴散體之間(128a,128b);一銲墊(114),其係連接至該等複數個 P+擴散體(116);以及一連接(120),其係連接至該等複數個 P+擴散體(116);以及一連接(120),其係連接至該等

- 19. 如請求項 18 之靜電放電保護結構,其中該銲墊係使用一第一複數個 導電通孔連接至該複數個 P+擴散體。

- 20. 如請求項 18 之靜電放電保護結構,其中連接至該第二 N+擴散體之該連接係使用一第二複數個導電通孔。

- 21. 如請求項19之靜電放電保護結構,其中該第一複數個導電通孔為金屬。

- 22. 如請求項 19 之靜電放電保護結構,其中該第一複數個導電通孔包含導電半導體矽。

- 23. 如請求項 20 之靜電放電保護結構,其中該第二複數個導電通孔為金屬。

- 24. 如請求項 20 之靜電放電保護結構,其中該第二複數個導電通孔包含導電半導體矽。

- 25. 如請求項 18 之靜電放電保護結構,其中該 P-井係耦合至接地。

- 26. 如請求項 18 之靜電放電保護結構,其中該 P-井係耦合至一共用的電源供應軌。

- 27. 如請求項 18 之靜電放電保護結構,其中該等複數個 P+擴散體、該第 N+擴散體以及該 N-井係實質上位於該銲墊之下。

- 28. 一種用於保護積體電路免受靜電放電損壞的系統,該系統包含:一靜電放電保護結構(100),其用於一積體電路之複數個輸入與輸出連接之至少一個連接,其中該靜電放電保護結構,包含:一積體電路,其具有一較輕摻雜的p型矽井(P-井)(132);一位於該P-井(132)中之較輕摻雜的n型矽井(N-井)(130);複數個位於該N-井(130)

中之較重摻雜的 p型矽擴散體(P+擴散體)(126);一位於該 N-井(130) 中之第一較重摻雜的 n型矽擴散體(N+擴散體)(128a),其中該第一 N+擴散體(128a) 圍繞該複數個 P+擴散體(126),並將該 N-井重疊進該 P-井(132);一位於該 P-井(132)中之第二較重摻雜的 n型 矽擴散體(N+擴散體)(128b),其中該第二 N+擴散體圍繞(128b)該第一 N+擴散體(128a);一銲墊(114),其係連接至該複數個 P+擴散體(126);以及一連接(120),其係連接至該第二 N+擴散體(128b)。

## (二)舉發證據之技術內容

#### 1. 舉發證據 2

證據 2 揭示一種靜電放電 (ESD) 保護電路,該電路包含在信號輸入和電源端間以背對背串聯之二極體,其允許該輸出信號升高至相對於供應電源上之一選擇距離且不會觸發該 ESD 電路。該 ESD 電路係以積體電路形式形成,其具有包含一對形成於 N 井中之 P+區域,或各別的 P+區域與各別的 N 井以形成 PN 接面的二極體,該二極體亦可以形成於在場二極體區域上之多晶矽層上,而第二對背對背的二極體可以選擇性地被連接於信號輸入端及接地之間,如此可允許該輸出信號下落至相對於接地電位之一選擇距離且也不會觸發該 ESD 電路。

## 2. 舉發證據 3

證據 3 揭示一個嵌入式寄生矽控整流器 (parasitic silicon controlled rectifier, parasitic SCR) 保護裝置,用於利用在汲極邊插入一 P+擴散體及一 N-井以保護一晶片或一輸出銲墊,其中該汲極之部份形成一低觸發 SCR。該裝置之布局使得該汲極連接在該 P+擴散體及該 N+汲極處緊綁一起,讓連接非常短;藉此防止閂鎖 (latch-up)。

#### 3. 舉發證據 4

證據 4 揭示一個輸出緩衝器,其包含一拉高電路及一拉低電路;其中該拉低電路具有一電阻,一二極體及一靜電保護元件。

#### 4. 舉發證據 5

證據 5 揭示在供應電源及接地端點之間加入保護電路,在半導體電路的內部元件仍常常損壞。在證據 5 之發明中,因於具有負電位的靜電的施加,就可以使進入到接地端點 TG 一側來的電荷易於通過電源端點 TV 向電源電壓 Vcc 放出,就可以防止內部元件因靜電引起之損壞。同樣地,證據 5 提供一保護電路,其可導向在電源端點及接地端點之間的電荷。

## 5. 舉發證據 6

證據 6 揭示一薄膜電晶體,用於一抗靜電電路及防止接面漏電流 (junction-leakage current)。

#### 6. 舉發證據 7

證據7揭示一種半導體裝置的靜電保護電路及其結構。證據7之特徵 在於該半導體裝置可與一銲墊連接,而該靜電保護結構用在一電晶體 汲極擴散區之淺摻雜電阻或擷取電阻,以使在靜電電壓從該銲墊輸入 時,在該電阻處產生壓降,進而形成一寄生雙極電晶體,以傳導因該 靜電放電產生之電流。

## 7. 舉發證據 8

證據 8 揭示之靜電放電(ESD)保護組件,其可被串接以提高 ESD 保護組件的總維持電壓且避免閂鎖。

#### 8. 舉發證據 9

證據 9 揭示一形成於一井中之保護電路,且與埋層連接。為改良保護 雙極電晶體被晶片佈局及晶片雜質濃度的影響,證據 9 提供一靜電損 壞保護裝置,其具有高靜電崩潰阻抗,高門鎖電阻抗以及良好的保護 能力。

## 9. 舉發證據 10

證據 10 揭示一靜電放電保護電路及其佈局;其中至少在電極墊及接地線之間具有一個靜電放電保護電路。

#### 10. 舉發證據 11

證據11揭示一用於半導體輸入裝置的靜電放電保護之製造方法。證據11提供一保護電路用於限制靜電電壓至一安全位準,且不破壞欲保護之電路及保護電路本身。在證據11之發明中,小靜電電壓被利用以產生電荷載體,其可用於觸發一蕭特基夾鉗二極體(Schottky clamp diode),藉此限制該靜電電壓至一低於100伏特崩潰電壓之大小。

- (三)舉發證據 2 結合舉發證據 3 尚難證明系爭專利申請專利範圍第 1、18 及 28 及 8-14、17、19-24 及 27 項之進步性。

- 1. 比較系爭專利圖 1 與證據 2 之 FIG. 9A 圖,證據 2 之 N+擴散體 912 係位於 N 井 910 內,而 N+擴散體 916 係位於 P 井 902 中,且擴散體 912 藉由金屬層 918 連接至 VCC,擴散體 916 藉由金屬層 924 連接至金屬層 914 再連接至 VIN,可知證據 2 之擴散體 912 係位於 N 井,擴散體 916 係位於 P 井,二者係屬不同的擴散體結構,與系爭專利之第二較重掺雜的 n 型矽擴散體(N+擴散體)均係位於 P 井中,二者結構顯然互異。再者,系爭專利之第二 N+擴散體係圍繞該第一 N+擴散體;惟證據 2 之圖 9A 並未揭示擴散體 912 及擴散體 916 圍繞第一 N+擴散體之結構;且根據證據 2 圖 9A 及說明書第 6 欄第 55 至 57 行之敘述,N+區域 916 形成二極體 D1,以及二極體 D3 與區域 912 及 915 形成於 N-井 910 中;故區域 912 必然侷限於 N-井 910 中以形成二極體 D3,而區域 916 則明顯地在 N-井 910 外部。再觀證據 2 圖式第 10A 圖 (為第 9A 圖等效電路圖) 及說明書第 8 欄第 10-13 行描述,可知在此相等之電路中顯示該二極體 D1 之陰極並未連接該二極體 D3(證據 2 圖式第 10A 圖中錯標

- 為 D4)之陰極,而該二極體 D3 之陰極係與 VCC 耦接,而該二極體 D1 之陰極係與 VIN 耦接,且該等陰極係耦接至不同之電位,故 912 及 916 為兩不同之摻雜區域,且彼此並未連接在一起以圍繞結構 904。益證證據 2 之 912 及 916 係位於不同區域之不同擴散體,且未連接而「圍繞」該第一 N+擴散體。

- 2. 系爭專利之銲墊與證據 2 之金屬層 (914、924、918)均作為積體電路間或路與外部連結之構件,兩者應屬具有相同功能之構件,原告訴稱證據 2 並未揭示系爭專利之銲墊結構云云,固非可採;惟系爭專利之複數個 P+擴散體係由一銲墊 114 連接,而證據 2 之 P+擴散體 906 係藉由金屬層 924 與金屬層 914 連接再接至 VIN,而 P+擴散體 908 藉由金屬層 918 連接至 VCC,因 VIN與 VCC 為兩不同電壓,故證據 2 之 P+擴散體 908, 906 係連接兩個不同之銲墊,與系爭專利之複數個 P+擴散體連接一銲墊不同。又系爭專利之第二 N+擴散體係連接至一連接,而證據 2 之擴散體 912 藉由金屬層 918 連接至 VCC,而擴散體 916 藉由金屬層 924 連接至金屬層 914 再連接至 VIN,因 VIN與 VCC 兩不同電壓,故金屬層 924 與金屬層 914 為兩不同之金屬層之連接,與系爭專利之第二 N+擴散體係連接至一連接,為不同之金屬層之連接,與系爭專利之第二 N+擴散體係連接至一連接,為不同之連接結構,故系爭專利之銲墊結構與連接結構與證據 2 之結構並不相同。

- 3. 證據 3 說明書第 4 欄第 1-62 頁雖已揭示一個嵌入式寄生矽控整流器 (parasitic silicon controlled rectifier, parasitic SCR)保護裝 置,用於利用在汲極邊插入一 P+擴散體及一 N-井以保護一晶片或一輸 出銲墊,其中該汲極之部份形成一低觸發 SCR;該裝置之布局使得該 汲極連接在該 P+擴散體及該 N+汲極處緊綁一起,讓連接非常短;藉此 防止閂鎖(latch-up);再參考證據3圖6亦可知證據3之N+擴散體620、 624 形成於 N 井層, 該 N 井則「重疊」形成於 P 井 21。惟查,由證據 3之圖 5 及圖 6 及說明書相關描述,可知 N+擴散體結構元件 620 及 624 為電晶體 T1 及電晶體 T2 之汲極(Drain),N+擴散體結構元件 616 及 628 為電晶體 T1 及電晶體 T2 之源極(Source),620 及 624、616 及 628, 二者應為分開的結構,且由圖 5 及 6 所示證據 3 亦無揭示結構元件 616 及 628 圍繞 N-井結構 612,由證據3圖5顯示的每個結構均為位於該 N-井 612 各邊之條帶,結構元件 620 及 624 為分開的結構,亦無圍繞 該 P+結構 622;此三個結構均為條帶狀,並被配置為彼此相鄰,故證 據 3 雖揭示 N+ (620,624) 形成於 N 井並將 N 井重疊進 P 井 21,惟其 並未揭示構件 620 及 624 圍繞 622 之結構,亦未揭示構件 616 及 628 圍繞 620 及 624 之技術特徵,至為灼然。

- 4. 基上說明,證據2雖揭示N+擴散體圍繞P+908之技術特徵,惟其未揭示系爭專利N+擴散層將N井重疊進P井21之技術特徵,而證據3雖揭示N+擴散層將N井重疊進P井21之技術特徵,惟證據3之N井中

P+擴散層僅為單一個,與系爭專利 N 井中具有複數個 P+擴散層不同, 且證據 3 之元件 620、622 及 624 為條帶狀且彼此相鄰與證據 2 之結構 不同,再者,證據3之主要技術特徵之一在於在P+擴散體之汲極與N+ 汲極係連接在一起,因此,元件 620、622 及 624 均藉由傳導構件而連 接至晶片墊38而具有相同之電位(參見證據3之說明書第3欄第51-52 行及第 4 欄第 21-22 行)。相較於證據 2,由於 N+擴散體係在元件 904 中浮動,元件 906(P+)係經由一金屬層 924 連接至元件 916(N+),且元 件 908(P+)係經由一金屬層 918 連接至元件 912(N+), 故可知元件 904 中之 N+擴散體、元件 906 及 908 顯然具有不同之電位,故證據 2 之 P+(908)與N+擴散體及證據3之P+(622)與N+(620,624)之連接方式 不同,故其結合上即有困難,即便結合證據2及證據3,其與系爭專 利之複數個 P+擴散體(126)藉由一銲墊連接結構亦不相同,且證據 2 及證據3均未揭示系爭專利之第二N+擴散體(128b)圍繞第一N+擴散 體(128a)之技術特徵,雖證據2及證據3均為ESD電路結構,惟從 事半導體電路製造設計領域者皆知,電路結構佈設不同,或元件間之 連接關係(方式)不同,其效果則會不同,因證據2及證據3與系爭 專利間存在前述之差異,故證據2及證據3之結合上並非明顯,且證 據2及證據3均未揭示系爭專利之第二N+擴散體(128b)圍繞第一N+ 擴散體(128a)之技術特徵。故證據2及證據3之組合尚無法證明系 爭專利請求項1、18及28項不具進步性。

- 5. 系爭專利申請專利範圍第 8-14、17、19-24 及 27 項為附屬項,其為獨立項之進一步限縮,因證據 2 及證據 3 之組合尚難證明系爭專利請求項 1、18 及 28 項不具進步性,故證據 2 及證據 3 之組合亦難證明系爭專利附屬請求項 8-14、17、19-24 及 27 項不具進步性。

- (四)舉發證據 2 結合舉發證據 3、4-11 尚難證明系爭專利申請專利範圍第 2 項不具進步性。

- 系爭專利申請專利範圍第2項為附屬項,其限定請求項1之「P-井係該積體電路基板」,而原舉發理由及原處分略以「證據3至11揭示該附屬技術特徵,故證據2及證據3、或證據2及證據4至11之組合可證明系爭專利請求項2不具進步性」云云。經查證據2及證據3之組合既難證明系爭專利請求項1不具進步性,已如前述,故證據2及證據3之組合尚難證明系爭專利請求項2不具進步性,因證據4至11係揭露系爭專利請求項2之附屬項之技術特徵,其並未揭示系爭專利請求項1之技術特徵,故由證據2、3結合證據4至11尚難證明系爭專利請求項2不具進步性。

- (五)舉發證據2結合舉發證據3、4或9尚難證明系爭專利申請專利範圍第3項不具進步性。

系爭專利申請專利範圍第3項為附屬項,除包含請求項1之技術特徵外,更進一步包含「一位於該第一與第二擴散體之間的場氧化層」,而原舉發理由及原處分略以「證據2、4或9揭示該附屬技術特徵,故證據2、3及證據4或9之組合可證明系爭專利請求項3不具進步性」云云。經查證據2及證據3之組合尚難證明系爭專利請求項1不具進步性,已如前述,且證據4或9係揭露系爭專利請求項3之附屬項之技術特徵,其並未揭示系爭專利請求項1之技術特徵,故由證據2、3結合證據4或9尚難證明系爭專利請求項3不具進步性。

- (六)舉發證據2結合舉發證據3、4尚難證明系爭專利申請專利範圍第4、 16及26項不具進步性。

- 1. 系爭專利申請專利範圍第4項附屬項,除包含請求項1之技術特徵外, 更進一步包含「該積體電路之一較輕摻雜的 n 型矽基板(N-基板),其中 該P-井係在該 N-基板中」,原舉發理由及原處分略以「證據4揭示該 附屬技術特徵,故證據2、3及4之組合可證明系爭專利請求項4不具 進步性」云云。經查證據2及證據3之組合尚難證明系爭專利請求項 1不具進步性,已如前述,且證據4係揭露系爭專利請求項4之附屬 項之技術特徵,其並未揭示系爭專利請求項1之技術特徵,故由證據 2結合證據3、4尚難證明系爭專利請求項4不具進步性。

- 2. 系爭專利申請專利範圍第 16、26 項為附屬項,其更進一步限定獨立項之「該 P-井係耦合至一共用的電源供應軌」,原處分及訴願決定略以「證據 4 已揭示該附屬技術特徵,故證據 2、3 及證據 4 之組合可證明系爭專利請求項 6、16 不具進步性」云云。惟查證據 2 及證據 3 之組合尚難證明系爭專利請求項 1、18 不具進步性,已如前述,且證據 4 係揭露系爭專利請求項 16、26 之附屬項之技術特徵,其並未揭示系爭專利請求項 1、18 之技術特徵,故由證據 2 結合證據 3 及 4 尚難證明系爭專利請求項 16、26 項不具進步性。

- (七)舉發證據2結合舉發證據3、4或10尚難證明系爭專利申請專利範圍第5-7項不具進步性。

- 系爭專利申請專利範圍第5至7項為附屬項,其更限定獨立項1之「複數個P+擴散體為帶狀、矩形或方形」,原舉發理由及原處分略以「證據2、3、4或10揭示該附屬技術特徵,故證據2、3、4或10之組合可證明系爭專利請求項5至7不具進步性」云云。經查證據2及證據3之組合尚難證明系爭專利請求項1不具進步性,已如前述,且證據4或10係揭露系爭專利請求項5至7之附屬項之技術特徵,其並未揭示系爭專利請求項1之技術特徵,故由證據2及3、4或10之組合尚難證明系爭專利請求項5至7不具進步性。

- (八)舉發證據 2 結合舉發證據 3、5、7、11 尚難證明系爭專利申請專利範 圍第 15、25 項不具進步性。

系爭專利申請專利範圍第15、25項為附屬項,其更限定獨立項1、18之「P井係耦合至接地」,而原舉發理由及原處分略以「證據3、5、7或11揭示該附屬技術特徵,故證據2及3、5、7或11之組合可證明系爭專利請求項15及25不具進步性」云云。經查證據2及證據3之組合尚難證明系爭專利請求項1、18不具進步性,已如前述,且證據5、7或11係揭露系爭專利請求項15或25之附屬項之技術特徵,其並未揭示系爭專利請求項1、18之技術特徵,故由證據2及3、5、7或11之組合尚難證明系爭專利請求項15及25不具進步性。

## 四、判決結果

綜上所述,舉發證據 2 結合舉發證據 3 尚難證明系爭專利申請專利範圍第 1、18 及 28 及 8-14、17、19-24 及 27 項不具進步性;舉發證據 2 結合舉發證據 3、4-11 尚難證明系爭專利申請專利範圍第 2 項不具進步性;舉發證據 2 結合舉發證據 3、4 或 9 尚難證明系爭專利申請專利範圍第 3 項不具進步性;舉發證據 2 結合舉發證據 3、4 尚難證明系爭專利申請專利範圍第 4、16 及 26 項不具進步性;舉發證據 2 結合舉發證據 3、4 或 10 尚難證明系爭專利申請專利範圍第 5-7 項不具進步性;舉發證據 2 結合舉發證據 3、5、7、11 尚難證明系爭專利申請專利範圍第 15、25 項不具進步性。換言之,參加人所提舉發證據,均不足以證明系爭專利不具進步性。換言之,參加人所提舉發證據,均不足以證明系爭專利不具進步性。從而,被告以系爭專利違反核准時專利法第 22 條第 4 項進步性之規定,而為「舉發成立,應撤銷專利權」之處分,即有未洽,訴願決定未加糾正而予維持,亦有未合。原告訴請撤銷訴願決定及原處分,為有理由,應予准許。

#### 五、智慧局分析檢討

本案中對於證據2與系爭專利之技術比對原處分有部分之認定與法院認定見解不同,原處分依據證據2之圖式所顯示之內容與系爭專利請求項之技術特徵作比對,有部分忽略了圖式中之構件是否符合系爭專利請求項中所定義之構件,此為原處分有所疏忽之處。再者,原處分因認定證據2與證據3已揭示系爭專利之所有技術特徵下,認定證據2與證據3間之組合並非困難,惟法院從證據2與系爭專利間存在4項結構上差異,且因證據2與證據3之結構及連接方式不同,故認定證據2與證據3之結合上應有困難,而原處分認定兩者之組合應無困難,亦略顯牽強。再者,即使將證據2與證據3組合亦有未揭示系爭專利之部分技術特徵,故證據2與證據3之組合尚無法證明系爭專利不具進步性。

# 附圖

# (一) 系爭專利之圖式

圖 1a 說明根據系爭發明一示範性具體實施例之一靜電放電保護結構之一斷面正視示意圖 B b 說明圖 1a 所示的靜電放電保護結構之平面示意圖

# (二)舉發證據2之圖式

FIG. 9A

# (三)舉發證據3之圖式

FIG. 5